## REFERENCES

- [1] P. Basile et al. "Solid state antenna switching," *RCA Rev.*, vol. 42, p. 752, Dec. 1981.

- [2] M. Caulton, A. Rosen, P. Stabile, and A. Gombar, "p-i-n diodes for low frequency high-power switching applications," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, p. 875, June 1982.

- [3] D. Leenov, "The silicon PIN diode as a microwave radar protector at megawatt levels," *IEEE Trans. Electron Devices*, vol. ED-11, pp. 53-61, Feb. 1964.

- [4] R. Caverly and G. Hiller, "Distortion in p-i-n diode control circuits," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-35, p. 492, May 1987.

- [5] G. Hiller and R. Caverly, "Predict PIN-diode switch distortion," *Microwaves and RF*, vol. 25, p. 111, Jan 1986.

- [6] R. Caverly, "A nonlinear p-i-n diode model for use in multi-diode microwave and RF communication circuit simulation," in *Proc. 1988 IEEE Int. Symp. Circuits Syst.*, June 1988, pp. 2295-2299.

- [7] J. Nordman and R. Greiner, "The small-signal inductive effect in a long PIN diode," *IEEE Trans. Electron Devices*, vol. ED-10, p. 171, 1963.

- [8] N. Prima and Y. Tkhorik, "Total impedance of a p-i-n diode at high injection levels," *Sov. Phys.-Semicond.*, vol. 1, no. 4, p. 444, Oct. 1967.

- [9] R. Varshney, D. Roulston, and S. Chamberlain, "Some properties concerning the a.c. impedance of P-I-N and P-N-N<sup>+</sup> diodes," *Solid-State Electron.*, vol. 17, p. 699, 1974.

- [10] R. Garver, *Microwave Diode Control Devices*. Dedham, MA: Artech House, 1976, pp. 326-329.

- [11] R. Caverly and G. Hiller, "Microwave resistance of gallium arsenide and silicon p-i-n diodes," in *1987 IEEE MTT-S Int. Microwave Symp. Dig.*, p. 591.

- [12] C. Barratt et al. "New GaAs PIN diodes with lower dissipation loss, faster switching speed at lower drive power," in *1983 IEEE MTT-S Int. Microwave Symp. Dig.*, p. 507.

- [13] J. White, *Semiconductor Control*. Dedham, MA: Artech House, 1977.

- [14] S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. New York: Wiley, 1981.

- [15] W. Reiss, "Volterra series representation of a forward biased p-i-n diode," *IEEE Trans. Electron Devices*, vol. ED-28, p. 1495, Dec 1981

## Development and Evaluation of a GaAs MMIC Phase-Locked Loop Chip Set for Space Applications

JOHN ARCHER, MEMBER, IEEE, BRYCE M. SMITH,

GARY R. WEAVER, HARRY WONG, MEMBER, IEEE,

AND JEFFRY Y. YONEMURA

**Abstract** — GaAs monolithic microwave integrated circuit (MMIC) chips designed for a phase-locked loop frequency source to be used in space applications have been developed. The chip set includes a three-stage resistive feedback amplifier (RFA) with 13 dB gain in a 275 MHz to 5.85 GHz bandwidth, a 2.0 GHz voltage-controlled oscillator (VCO), a 2.8 GHz digital prescaler, and a VHF/UHF digital phase/frequency discriminator. Both analog and buffered-FET logic (BFL) digital circuits were fabricated on the same wafer. The MMIC process which was developed for this application comprises molecular beam epitaxial (MBE) deposition of the active layer, proton isolation, submicron gates, thin-film TaN resistor deposition, and silicon nitride passivation. The chip set was used successfully to implement a 2.0 GHz all-GaAs phase-locked loop (PLL).

### I. INTRODUCTION

MMIC's will have a major impact on communication satellite payloads of the future. One area of direct application is in fixed-frequency local oscillators (LO's) which are used for frequency mixing circuits throughout modern payloads. Conven-

Manuscript received March 7, 1988; revised October 25, 1988.

J. Archer is with the Varian III-V Device Center, 3251 Olcott St., Santa Clara, CA 95050.

B. M. Smith, G. R. Weaver, H. Wong, and J. Y. Yonemura are with the Space and Communications Group, Hughes Aircraft Company, P.O. Box 92919, Los Angeles, CA 90009.

IEEE Log Number 8826049.

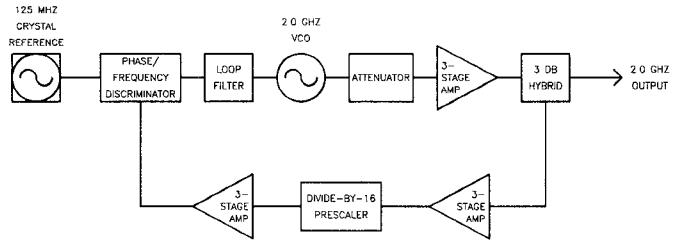

Fig. 1 GaAs MMIC phase-locked loop block diagram

tional hybrid LO's are both bulky and heavy, making them highly unsuitable for phased array antenna applications.

Development of a generic GaAs PLL chip would greatly reduce the weight, size, and cost of an LO reference source while providing inherent radiation hardness. The stabilization of a microwave frequency source and the reduction of off-carrier noise density by means of a crystal oscillator and PLL have been described by Ohira et al. [1]. Additionally, MMIC chips suitable for use in PLL's have been reported [2]-[5]. In this paper, the implementation of MMIC's in a GaAs PLL integrated on a single breadboard is described. The basic analog and digital building blocks (the RFA, prescaler, VCO, and phase/frequency discriminator) have been fabricated monolithically on a single GaAs wafer and assembled into a MMIC PLL. The PLL design approach, processing technology, individual chip results, loop integration, and noise reduction will be discussed.

### II. PHASE-LOCKED LOOP DESIGN

The primary goal of this project was to develop a 2.0 GHz MMIC PLL chip for use as an LO in satellite payloads. By designing a PLL with a wide capture range, a generic LO chip could be used in different satellite applications whereby the mere selection of a crystal reference would determine the LO frequency. Fig. 1 shows a block diagram of the MMIC/MIC phase-locked loop developed to this point. The PLL is a classical second-order design having passive *RC* loop filtering. The PLL has a 125 MHz crystal reference source that feeds the digital phase/frequency discriminator. A 2.0 GHz common-gate VCO provides the PLL microwave signal, while resistive-feedback amplifiers (RFA's) supply gain where needed in the loop. A prescaler scales the 2.0 GHz signal for feedback into the phase/frequency discriminator.

### III. PROCESS DESCRIPTION

The process developed for the fabrication of the chips described in this paper comprises the following features:

- molecular beam epitaxial (MBE) deposition of the active layer,

- isolation of the active regions by proton-induced damage,

- thin-film tantalum nitride resistors,

- 0.75- $\mu$ m-gate FET's,

- Schottky level-shifting diodes,

- metal-insulator-metal (MIM) capacitors with silicon nitride dielectric,

- air bridge second level interconnections (Fig. 2),

- silicon nitride passivation.

The MBE material, deposited sequentially on an undoped semi-insulating substrate, consists of a 0.4- $\mu$ m-thick undoped

Fig. 2. SEM of second level air bridge metallization.

TABLE I

PCM TEST RESULTS

(MEAN  $\pm$  STANDARD DEVIATION ACROSS THE WAFER)

|                                    |                                                             |

|------------------------------------|-------------------------------------------------------------|

| Saturated drain current, $I_{DSS}$ | $161 \pm 81 \text{ mA/mm}^2$                                |

| Transconductance, $g_m$            | $195 \pm 29 \text{ mS/mm}$                                  |

| Pinch-off voltage, $V_{p0}$        | $0.96 \pm 0.51 \text{ V}$                                   |

| Gate metal resistance              | $84.7 \pm 7.7 \text{ ohm/mm}$                               |

| Ohmic Contact resistance           | $0.065 \pm 0.004 \text{ ohm-mm}$                            |

| Sheet resistance of MBE layer      | $110.3 \pm 4.2 \text{ ohm/sq.}$                             |

| Active layer carrier concentration | $3.9 \times 10^{17} \pm 1.9 \times 10^{16} \text{ cm}^{-3}$ |

| Active layer carrier mobility      | $2870 \pm 153 \text{ cm}^2/\text{Vs}$                       |

| Tantalum nitride sheet resistance  | $49.3 \pm 5.3 \text{ ohm/sq.}$                              |

| MIM capacitance/area               | $243 \pm 3 \text{ pF/mm}^2$                                 |

buffer layer; a  $0.18\text{-}\mu\text{m}$ -thick,  $4 \times 10^{17} \text{ cm}^{-3}$  silicon-doped active layer; and a  $0.12\text{-}\mu\text{m}$ -thick  $2 \times 10^{18} \text{ cm}^{-3}$  silicon-doped n+ layer to provide low-resistance ohmic contacts. The advantages of MBE include the possibility of selective deposition and integration of FET's and varactors requiring different doping profiles on the same chip. This is important for the final monolithic integration of the PLL. The completed wafer is lapped and polished to a final thickness of  $400 \mu\text{m}$  and the back side is metallized with Ti-W/Au suitable for eutectic bonding of the chips into the final assembly.

The resistors, FET's, and diodes are passivated by a silicon nitride film deposited after the first-level metal interconnections have been completed. This silicon nitride film also provides the dielectric material for the MIM capacitors. The thin-film tantalum nitride resistors have a sheet resistance of  $50 \text{ ohms/sq.}$ , a temperature coefficient of resistance in the range of  $-60$  to  $+30 \text{ ppm}$ , and are stable to at least  $210^\circ\text{C}$  at the maximum rated current density of  $0.5 \text{ mA}/\mu\text{m}$ .

The process was characterized and monitored by means of a test pattern chip or process control monitor (PCM) similar to that described by Immorlica *et al.* [6]. The final PCM test results are presented in Table I. A  $728 \mu\text{m}$  gate width FET was included on the PCM chip. This FET exhibited  $f_t = 17 \text{ GHz}$ ,  $f_{\text{max}} = 40 \text{ GHz}$ , and a maximum available gain of  $7.5 \text{ dB}$  at  $8 \text{ GHz}$ .

#### IV. RESISTIVE-FEEDBACK AMPLIFIER CHIP

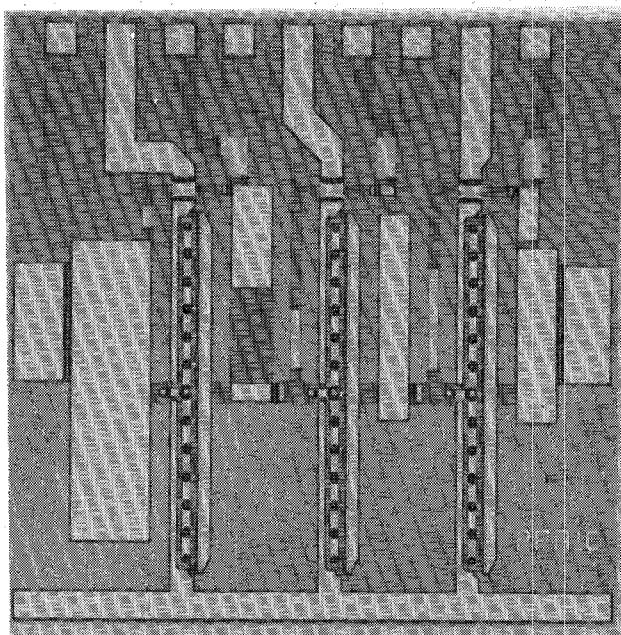

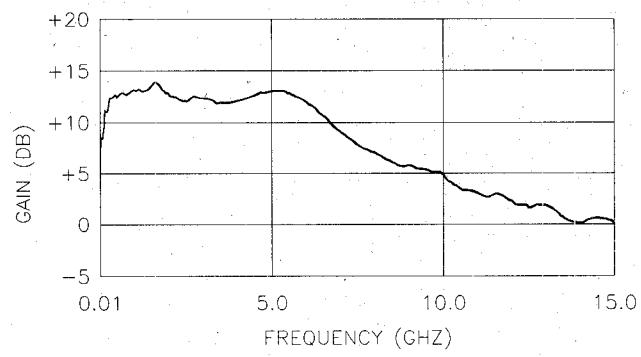

The monolithic RFA consists of three resistive feedback stages using  $728 \mu\text{m}$  FET's in all three stages (Fig. 3(a)). The RFA typically displayed  $13 \text{ dB}$  gain with peak-to-peak ripple not

(a)

(b)

Fig. 3. (a) Three-stage resistive feedback amplifier ( $1.63 \text{ mm} \times 1.65 \text{ mm}$ ).

(b) Wide-band gain response of three-stage resistive feedback amplifier.

exceeding  $2 \text{ dB}$  from  $275 \text{ MHz}$  to  $5.85 \text{ GHz}$ . Usable amplifier gain was shown from  $10 \text{ MHz}$  to  $14.0 \text{ GHz}$  (Fig. 3(b)).

#### V. DIGITAL IC CHIPS

The digital phase/frequency discriminator [7] and the digital prescaler were previous Hughes designs that were modified to meet the requirements of our PLL. FET channel characteristics were modified for processing compatibility with the analog circuits on the wafer, and digital circuit topology was customized for use in the PLL. All digital circuits use standard BFL with high- and low-impedance outputs to drive various load conditions.

Circuit performances of the two devices were well within the needs of the PLL. The phase/frequency discriminator operated up to  $480 \text{ MHz}$ . In the PLL, the A and the B output were resistively summed to allow full  $180^\circ$  phase detection. The prescaler chip operated up to  $2.8 \text{ GHz}$ , an improvement well over the  $2.4 \text{ GHz}$  result achieved with a previous iteration. At the  $2.0 \text{ GHz}$  PLL operating frequency, the prescaler produces a  $-3 \text{ dBm}$  output signal at a power level of  $-3 \text{ dBm}$  with no harmonically related spurs within the band of interest.

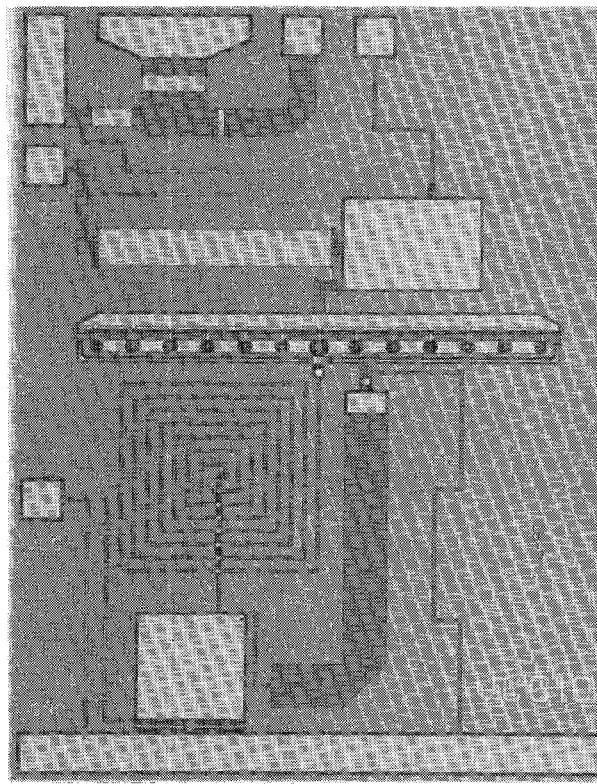

Fig. 4. Common-gate VCO (1.22 mm  $\times$  1.55 mm).

## VI. VOLTAGE-CONTROLLED OSCILLATOR CHIP

The VCO was initially realized as a MIC using bond wire inductance in series with the gate and the source of a  $728 \mu\text{m}$  FET to obtain negative resistance over the band of interest. The common-gate FET configuration uses gate bias to control the frequency of oscillation. After successful operation of this circuit, the MMIC was designed with the same topology using spiral inductors (Fig. 4). However, the original MIC VCO was utilized for all test results presented in this report. The VCO's band of operation is 1.9 to 2.2 GHz, with an output power of +5 dBm.

## VII. PHASE-LOCKED LOOP INTEGRATION

The PLL required the integration of nine circuit building blocks, each individually tested. Since ease of chip interchangeability of all circuits was desired, the monolithic chips were assembled onto individual 25 mil alumina substrates. The monolithic chips, the VCO, and a thin-film TaN 3 dB power splitter were integrated into the PLL housing. A first-order  $RC$  loop filter was inserted between the phase/frequency discriminator and VCO to control the overall loop response.

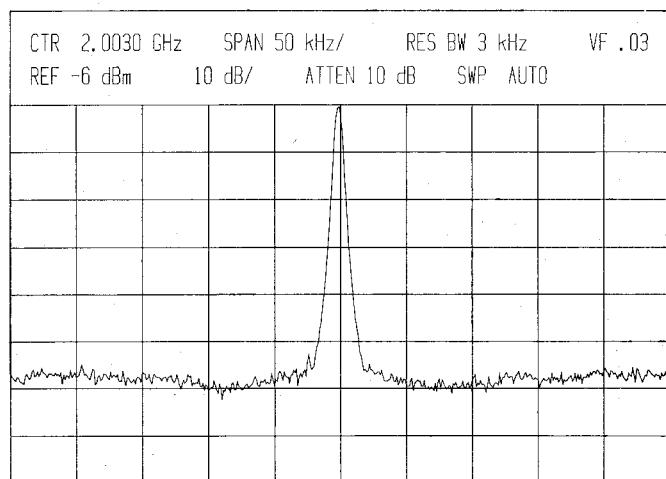

The locked loop, using an input reference frequency of 125 MHz, provided the 2 GHz spectrum plot shown in Fig. 5. Over the wide-band spectrum, no spurs were present. Under these operating conditions, preliminary phase noise performance of better than  $-70 \text{ dBc/Hz}$  at a 10 kHz offset was measured at an output power level of  $-6 \text{ dBm}$ . Total dc power consumption was 3 W. Lock range was limited to 350 kHz.

The PLL has the potential for improved performance by the incorporation of an active loop filter in place of the passive  $RC$  loop filter to increase the overall loop gain. The loop filter is the critical building block that determines the dynamic performance of the PLL. This includes the capture and lock ranges, band-

Fig. 5. Phase-locked loop performance.

width, and transient response. Because  $1/f$  noise inherent in GaAs is a problem, the loop filter dc amplifier may have to be implemented in silicon and located off-chip in the final design. Adjustment of the active loop filter compensator will allow control of the PLL tracking and phase noise performance.

## VIII. CONCLUSION

Analog and digital MMIC chips for a 2.0 GHz phase-locked loop have been developed for space applications. MBE processing techniques that were implemented allow excellent analog and digital MMIC compatibility. The MMIC chips were used successfully in a 2.0 GHz single-breadboard phase-locked loop with a noise level of less than  $-70 \text{ dBc/Hz}$  at a 10 kHz offset in a surface area of only  $8 \text{ cm}^2$ . The results attained by this research and development project should lead to further refinement of the PLL or development of a single-chip PLL.

## ACKNOWLEDGMENT

The authors would like to thank B. Walsh for his valued technical guidance and for giving them the opportunity to work on this program. They would also like to thank B. F. Adams, G. M. Mascia, L. Y. Ching, M. Orlovic, and C. Gamab for their contributions.

## REFERENCES

- [1] T. Ohira, T. Hiraoka and H. Kato, "MMIC 14-GHz VCO and Miller frequency divider for low-noise local oscillators," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-35, pp. 657-662, July 1987.

- [2] B. N. Scott and G. E. Brehm, "Monolithic voltage controlled oscillator for X- and Ku-bands," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 2172-2177, Dec. 1982.

- [3] T. Ohira, K. Araki, T. Tanaka, and H. Kato, "14 GHz band GaAs monolithic analogue frequency divider," *Electron. Lett.*, vol. 21, pp. 1057-1058, Oct. 1985.

- [4] K. Honjo and M. Madihian, "Novel design approach for X-band GaAs monolithic analog 1/4 frequency divider," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-34, pp. 435-441, Apr. 1986.

- [5] M. Madihian and K. Honjo, "GaAs-monolithic IC's for an X-band PLL-stabilized local source," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-34, pp. 707-713, June 1986.

- [6] A. A. Immorlica, D. R. Decker, and W. A. Hill, "A diagnostic pattern for GaAs FET material development and process monitoring," *IEEE Trans. Electron Devices*, vol. ED-27, pp. 2288-2291, Dec. 1980.

- [7] I. Shahriary, G. Des Brisay, S. Avery, and P. Gibson, "GaAs monolithic digital phase/frequency discriminator," in *1985 IEEE GaAs IC Symp. Tech. Dig.*, pp. 183-186.